# **PBGA-SD**

## Plastic Ball Grid Array - Stacked Die

## **Highlights**

Stacking of die enables more functionality and integration in a conventional PBGA package

#### **Features**

- Increased sub-system performance achieved by integrating multiple chips into a single package

- Die to die bonding capability for device/signal integration

- 15 x 15mm to 40 x 40mm body sizes available

- Ball counts up to >1000 balls

- 0.65, 0.80, 1.00, 1.27 and 1.5mm ball pitch

- SnPb and Pb-free balls available

- Full in-house design capability with wide range of custom and open tool designs

- Full in-house electrical, thermal and mechanical simulation and measurements capability

- Multiple chip design and optional passive/discrete components available

- Standard 2, 4 and 6 layer substrates as well as high density substrate options

- Pb-free and green material set options

- Multiple routing layers and dedicated ground/power planes available for improved electrical and thermal performance

## **Applications**

- DSPs and Memory

- Gate Arrays

- ASICs

- PC Chipsets and Peripherals

- Microprocessors/Controllers

## Description

BGA packages can be used for high performance applications with high I/O connections and high thermal and electrical requirements. The characteristics of BGA packages make them suitable for a wide variety of devices used in computing platforms, networking, hand-held consumer products, wireless communications devices, video cameras, home electronic devices and game consoles.

Our chip stack technology offers the flexibility of stacking 2 to 7 die in a single package. The Stacked Die Plastic Ball Grid Array (PBGA-SD) package takes advantage of the proven high electrical and thermal performance of PBGA packages, with efficient use of space made possible through die stacking technology. PBGA-SD packages use laminate substrates and are available in a variety of body sizes and ball counts, combining advanced assembly processes and proven material sets for enhanced yield, reliability and performance.

**Specifications**

Die Thickness 150-381μm (6-15mils)

Gold Wire 15-30μm (0.6/0.7/0.8/0.9/1.0/1.1/1.2mils)

diameter

Pd/Cu Wire 15-30µm (0.6/0.7/0.8/1.0mils) diameter

Bond Pad Pitch 45µm inline or 25/50µm staggered capable

Mold Cap Thickness 0.7-1.17mm

Marking Laser

Packing Options JEDEC tray/tape & reel

#### Reliability

Moisture Sensitivity Level

High Temperature Storage

**Pressure Cooker Test**

**Unbiased HAST**

Temperature Cycling Condition C (-65°C/150°C),

1000 cycles (typical)

150°C, 1000 hrs (typical)

121°C, 100% RH/2 atm, 168 hrs

JEDEC Level 3, 260°C reflow

Temperature/Humidity Test 85°C/85°C RH, 1000 hrs

130°C/85%, RH/2 atm, 96 hrs

### Thermal Performance θja (°C/W)

The thermal performance of each die in the stack is influenced by other die in the stack. Thermal performance is highly dependent on package size, die size, substrate layers and thickness, and solder ball configuration. Simulation for specific applications should be performed.

#### **Electrical Performance**

Electrical parasitic data is highly dependent on the package layout. 3D electrical simulation can be used on the specific package design to provide the best prediction of electrical behavior. First order approximations can be calculated using parasitics per unit length for the constituents of the signal path. Data below is for a frequency of 100MHz and assumes 1.0 mil gold bonding wire.

| Conductor<br>Component | Length<br>(mm) | Resistance<br>(mOhms) | Inductance<br>(nH) | Inductance<br>Mutual (nH) | Capacitance<br>(pF) | Capacitance<br>Mutual (pF) |

|------------------------|----------------|-----------------------|--------------------|---------------------------|---------------------|----------------------------|

| Wire                   | 2              | 120                   | 1.65               | 0.45 - 0.85               | 0.10                | 0.01 - 0.02                |

| Net (2L)               | 2 - 7          | 34 - 119              | 1.3 - 4.55         | 0.26 - 2.28               | 0.25 - 0.95         | 0.06 - 0.42                |

| Total (2L)             |                | 154 - 239             | 2.95 - 6.2         | 0.71 - 3.13               | 0.35 - 1.05         | 0.07 - 0.44                |

| Wire                   | 2              | 120                   | 1.65               | 0.45 - 0.85               | 0.10                | 0.01 - 0.02                |

| Net (4L)               | 2 - 7          | 34 - 119              | 0.90 - 3.15        | 0.18 - 1.58               | 0.35 - 1.10         | 0.06 - 0.42                |

| Total (4L)             |                | 154 - 239             | 2.55 - 4.80        | 0.63 - 2.43               | 0.45 - 1.20         | 0.07 - 0.44                |

Note: Net = Total Trace Length + Via + Solder Ball.

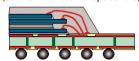

#### **Cross Section**

#### Package Size (mm) Ball Count

15 x 15 160, 176, 196

17 x 17 192, 196, 208, 217, 252, 256

17.2 x 17.2 512

31 x 31

35 x 35

19 x 19 272, 289, 292, 296, 297, 300, 301, 305, 324, 376

21 x 21 400, 456, 484

23 x 23 169, 192, 208, 217, 233, 241, 288, 301, 304, 305, 318, 320, 324, 338,

340, 348, 352, 360, 376, 385, 388, 420, 456, 480, 484, 492

27 x 27 225, 256, 272, 277, 292, 300, 312, 316, 320, 324, 336, 352, 384, 388,

400, 416, 456, 472, 480, 484, 496, 508, 512, 544, 580, 585, 636, 650, 676

304, 320, 353, 385, 421, 433, 434, 448, 458, 460, 480, 540, 556, 560, 564, 604, 608, 609, 640, 644, 652, 676, 688, 692, 701, 721, 772, 896

04, 312, 313, 340, 352, 385, 388, 400, 420, 426, 432, 448, 452, 454, 456, 458, 474, 480, 484, 492, 496, 512, 516, 532, 542, 544, 548, 556, 564, 573,

580, 611, 624, 640, 648, 661, 665, 676, 680, 688, 700, 716, 729, 736, 740,

748, 756, 792, 816, 824, 840, 867, 868, 1012, 1156

37.5 x 37.5 435, 480, 552, 600, 601, 625, 627, 685, 701, 785, 788, 804, 840, 841

40 x 40 503, 557, 569, 596, 600, 745, 776, 928, 961, 1253

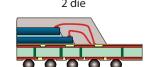

## **Package Configurations**

3 die (2 functional die + 1 spacer die)

4 die (3 functional die + 1 spacer die)